采用MAX II器件实现FPGA设计安全解决方案

发布时间:2016-03-25作者:智汇小新

本文提供的解决方案可防止FPGA设计被拷贝,即使配置比特流被捕获,也可以保证FPGA设计的安全性。这种安全性是通过在握手令牌由MAX II器件传送给FPGA之前,禁止用户设计功能来实现的。

基于SRAM的FPGA是易失器件,需要外部存储器来存储上电时发送给它们的配置数据。在传送期间,配置比特流可能会被捕获,用于配置其他FPGA。这种知识产权盗窃损害了设计人员的利益。

本文提供的解决方案可防止FPGA设计被拷贝,即使配置比特流被捕获,也可以保证FPGA设计的安全性。通过在握手令牌由MAX II器件传送给FPGA之前,禁止用户设计功能来实现这种安全性。选用MAX II器件来产生握手令牌,这是因为该器件具有非易失性,关电时可保持配置数据。而且,对于这种应用,MAX II器件是最具成本效益的CPLD。本文还介绍了采用这种方案的一个参考设计。

硬件实现

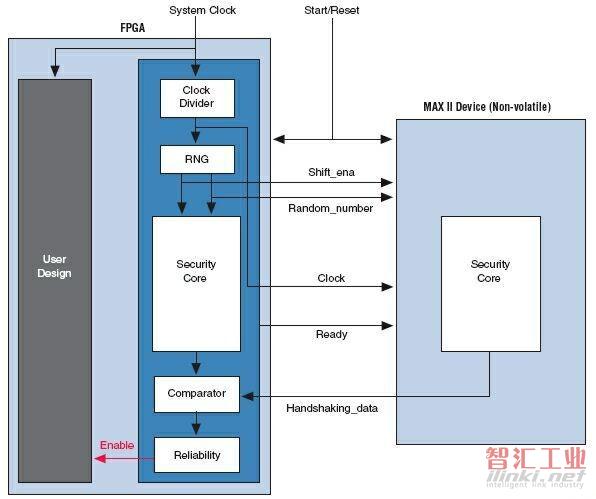

FPGA设计安全解决方案的硬件实现如图1所示。MAX II器件产生连续的握手令牌,发送至FPGA,以使能用户设计。FPGA和MAX II器件之间传送5个信号:clock、shift_ena、random_number、ready和handshaking_data。

一旦FPGA经过配置后,它向MAX II器件提供连续时钟。同时连接至FPGA和MAX II器件的启动/复位信号必须置位,以启动系统工作。FPGA中的随机数发生器(RNG)开始为FPGA和MAX II器件产生初始计数值(每次上电或者启动/复位信号置位时,仅向MAX II器件发送一次随机数)。随机数准备好后,shift_ena信号变为高电平,采用random_number信号,随机数串行移位至MAX II器件。随机数全部移位至MAX II器件后,ready信号置位,指示FPGA可以接收来自MAX II器件的握手令牌。

配置之后,由于Enable信号还是逻辑低电平,FPGA中的用户设计功能被禁止。只有MAX II器件送出的握手令牌和FPGA内部产生的数据相匹配,Enable信号才会置位,启动用户设计功能。这两个数据之间出现差异时,Enable信号变为低电平,禁止用户设计功能。MAX II器件中产生握手令牌和FPGA器件中产生数据的方法和过程相同。如果没有正确的令牌,FPGA器件中的用户设计功能被禁用。这样,即使配置比特流被捕获,也可以防止用户设计被拷贝。

图1:FPGA设计安全方案的硬件实现。

设计构建模块

FPGA的设计安全组成包括一个时钟分频器、随机数发生器(RNG)、安全内核、比较器和可靠性部分,而MAX II器件的设计安全组成只包括图1所示的安全内核。

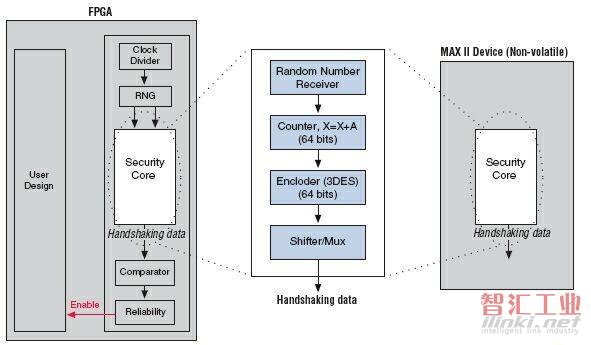

FPGA和MAX II器件使用的安全内核相同,如图2所示,由以下部分构成:随机数接收器、64位计数器、编码器、移位器/复用器。

图2:FPGA和MAX II器件的安全内核。

1、时钟分频器FPGA中的时钟分频器用于从系统时钟产生速率较低的时钟,供给FPGA和MAX II器件的安全内核使用。这是因为安全内核不需要运行在非常高的频率下。特别是当系统运行频率非常高时,时钟分频器的作用便比较显著,否则,如果系统运行频率较低,可以不使用该分频器。

2、随机数发生器(RNG)每次启动/复位信号置位时,RNG为64位计数器产生随机初始值。然后,随机数同时串行移位至FPGA和MAX II器件的安全内核。参考设计采用32位RNG。

3、随机数接收器随机数接收器接收来自RNG的串行随机数,并按照正确的顺序排列数据,将其做为初始值送入64位计数器。

4、64位计数器64位计数器用于产生送入编码器的64位数据。它是按照公式X=X+A进行的一个简单加法器。X是一个64位初始值,而A是计数器递增值,应为质数。初始值X来自RNG。参考设计中,32位来自RNG,其余32位由用户在设计代码中设置。A可以由用户在设计代码中设置。计数器输出送入编码器,对数据进行加密。编码器每次完成前一数据的加密后,计数器数值递增。

5、编码器编码器可以采用任何难以破译的加密标准。参考设计采用了三重数据加密标准(3DES)。3DES编码器的输入和输出是64位值,需要48个时钟周期完成64位数据加密。

6、移位器/复用器移位器/复用器将编码器输出比特(16位)的一部分按照特定顺序,存储在寄存器中,编码器准备下一数值时,将其串行移位至比较器。

7、比较器比较器将MAX II器件的编码数据(握手令牌)与FPGA内部产生的编码数据逐位比较。如果MAX II器件和FPGA的数据相匹配,Enable信号置位,使能用户设计功能。如果出现不匹配,请参见下面的可靠性保证一节。这种方式可以重复几次,以产生更多的Enable信号,使能用户设计的不同部分。这种重复方式可以防止有人篡改FPGA比特流(这种可能性较低),致使Enable信号变为高电平,导致设计安全方案失效。

8、可靠性可靠性部分处理随机比特错误,这种错误可能会导致系统停止工作。参考设计允许每10个时钟周期中出现一次数据不匹配(这仅仅是一个例子,用户可以根据实际应用,修改该方法,达到最佳效果)。换句话说,如果10个时钟周期中,数据不匹配不超过一次,Enable信号仍将保持高电平,系统继续工作。如果10个时钟周期中出现两个错误,那么,Enable信号变为低电平,禁止用户设计功能。在启动/复位信号置位,复位系统前,系统停止工作。

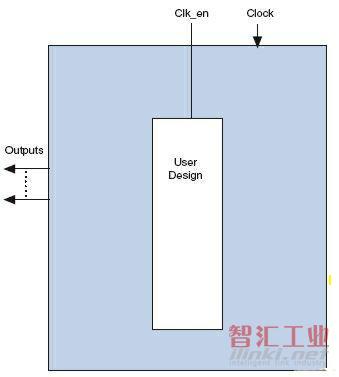

图3:不支持安全方案的FPGA设计。

用户设计模块

用户设计模块是真正的FPGA设计。来自安全模块的Enable信号低电平时用于禁止用户设计模块。换言之,如果比较器发现MAX II器件和FPGA的数据不匹配,考虑到可靠性之后,将禁止用户设计功能。

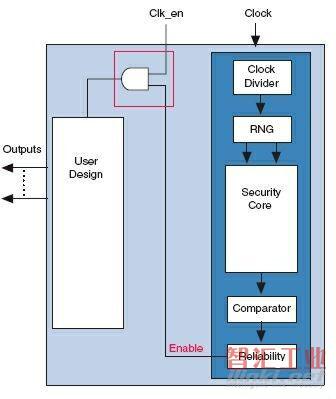

图3是Enable信号低电平时,禁止用户设计功能的实例。图3所示的FPGA用户设计具有Clk_en输入信号,用于使能设计中的时钟。只有Clk_en信号高电平时,才启动设计功能。为实现设计安全方案,对用户设计稍做修改(增加了一个AND逻辑门),这样,当来自安全模块的Enable信号低电平时,禁止用户设计,如图4所示。

解决方案的安全性

上电时,当FPGA的配置比特流由外部存储器传送至FPGA时,有可能被捕获。使用捕获的比特流来配置其他FPGA可以拷贝FPGA设计。

采用该解决方案,只有当MAX II器件的握手令牌与FPGA内部产生的数据相匹配时,FPGA用户设计才开始工作。由于被复制的设计在没有握手令牌时无法工作,因此保证了FPGA设计的拷贝安全性。用于产生握手令牌的MAX II器件具有非易失特性,关电时可保持其配置。

解决方案的安全性依赖于MAX II器件产生的握手令牌。要破解该方案,需要拷贝MAX II器件产生的全部令牌比特流,或者计算出编码器用于产生令牌的密钥。由于每次上电时,MAX II器件产生的握手令牌都不同,因此,拷贝全部比特流来破解该方案是不可能的。这在于采用了RNG,它在上电时产生不同的数值送给MAX II器件。

图4:支持安全方案的FPGA设计。

如果采用了成熟的加密算法,那么破解编码器使用的密钥将非常困难。而且,无法从外部看到编码器输入数据,只有一部分加密数据串行移出,更难实现纯文本攻击。纯文本攻击分析编码器的输入和输出数据,猜出密钥,实施攻击。因此,该解决方案保护了FPGA设计。

为保证该方案正常工作,安全模块的时钟应和FPGA用户设计的时钟一致,如图1所示。这样可以防止有人在Enable信号高电平时,禁用安全模块时钟。

本文小结

FPGA设计安全解决方案保护了Altera FPGA设计被拷贝(即使配置比特流被捕获)。在MAX II器件通过握手令牌验证前,禁止FPGA用户设计,实现了该解决方案。只有握手令牌与FPGA内部产生的数据匹配时,FPGA用户设计才被使能。该解决方案还保护了FPGA中的设计人员知识产权。

Copyright © 2015 ilinki.net Inc. All rights reserved. 智汇工业版权所有

电话:010-62314658 邮箱:service@ilinki.net

主办单位:智汇万联(北京)信息技术有限公司

主办单位:智汇万联(北京)信息技术有限公司