基于流水线技术的并行高效FIR滤波器设计

发布时间:2017-04-01作者:智汇小新

数字滤波器可以滤除多余的噪声,扩展信号频带,完成信号预调,改变信号的特定频谱分量,从而得到预期的结果。数字滤波器在DVB、无线通信等数字信号处理中有着广泛的应用。在数字信号处理中,传统滤波器通过高速乘法累加器实现,这种方法在下一个采样周期到来期间,只能进行有限操作,从而限制了带宽。现实中的信号都是以一定的序列进入处理器的,因此处理器在一个时钟周期内只能处理有限的位数,不能完全并行处理。基于并行流水线结构的FIR滤波器可以使笔者设计的64阶或者128阶滤波器与16阶滤波器的速度一样快,其显著特别是在算法的每一个阶段存取数据。FPGA结构使得以采样速率处理数字信号成为常数乘法器的理想载体,提高了整个系统的性能。由于设计要求的差异,如字长、各级输出的保留精度等不同,在整个设计过程中,各个环节也有所不同,这就需要根据不同的要求对数据进行不同的处理,如截断、扩展等,从而设计出既满足设计需要,又节省FPGA资源的电路。

1 FIR并行滤波器结构

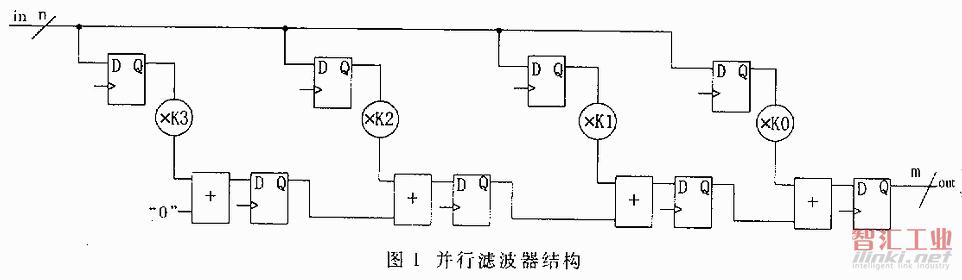

数字滤波器主要通过乘法器、加法器和移位寄存器实现。串行处理方式在阶数较大时,处理速度较慢。而现代数字信号处理要求能够快速、实时处理数据,并行处理数据能够提高信号处理能力,其结构如图1所示。

从上面的算法可以看出,处理数据的采样时钟对每一个抽头来说都是并行的,并且加法器和移位寄存器采用级联方式,完成了累加器的功能,综合了加法器和移位寄存器的优点,而且这种算法的各级结构相同,方便扩展,实现了任意阶数的滤波器。算法中,真正点用系统资源的是乘法器。如果将系数量化成二进制,就能采用移位寄存器和加法器实现乘法功能。对于一个特定的滤波器,由于它有固定的系数,乘法功能就是一个长数乘法器。下面将讨论乘法器的设计问题。

2 FIR并行滤波器的乘法器设计

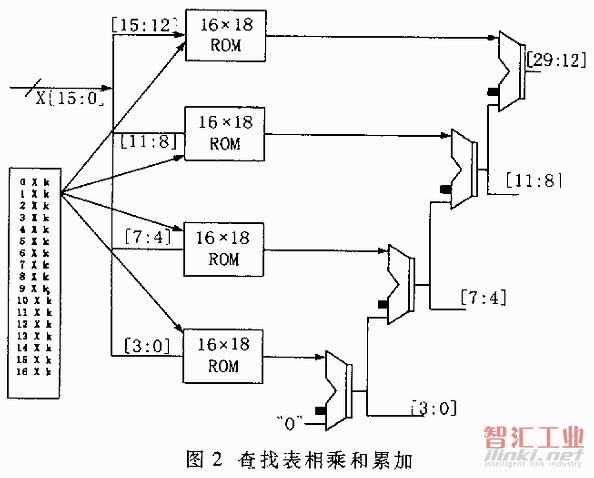

在并行滤波器的设计中,每一个乘法器的一端输入数据,另一端为固定常数。对于常数乘法器,可以预先将常数的部分乘积结构存储起来,然后通过查表的方式实现两个数据的乘积。以16位输入、常数为14位的乘法器为例,给出其实现结构如图2所示。

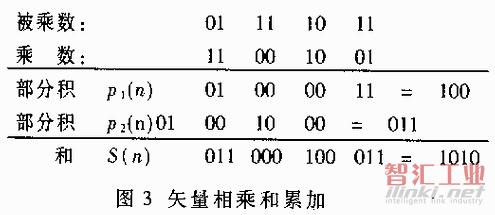

对于无符号数来说,这是一种理想结构。但是在实际使用中,通常使用有符号数且常用补码的形式,因此需要对这种结构进行改进。一种改进方法是将输入的数据分开,即最高的几位作为有符号数处理,其它作为无符号数处理。第二种改进方法是将符号数经过补码/原码变换器变换成原码,然后,将原码作为无符号数处理,通过有符号数的符号位来控制加法器的加减。第三种改进方法是一种优化方法,即要用三个二进制补码变换器,处理输入的有符号数和滤波器的系数,这样可以避免使用有符号数的乘法和加法运算。具体的乘法累加器运算过程及结果如图3所示。其中,对应乘数高位和低位部分积p1(n)和p2(2)可以分别先垂直相加后水平相加,或者先水平相加后垂直相加,最后的结果是一样的。若采用后种方法,由于FIR滤波器的h(n)均为常数,得到部分积的矢量乘法运算就演变成了查表法,其中,S1(n)表示S(n)的最低有效,p1表示最低有效位部分积之和。

同理,得p2,将p2左移一位与p1相加,便得到最后结果。这种查表法就是采用流水线技术进行FIR滤波器算法分解的基础,当字长增加时,相应得到p3、p4等。并相应移位相加即可。

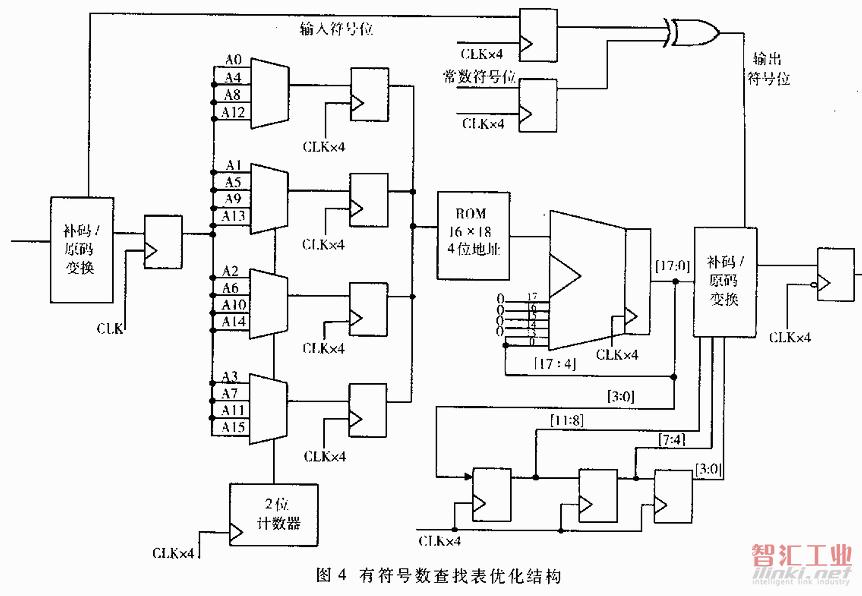

采用流水线技术和加法器的资源共享技术可以更好地提高常数乘法器的优越性。16比特输入、14比特常数的这种方法的常数乘法器的结构如图4所示。

在这种结构中,时钟是f1,内部操作的时钟是4×f1,其中的4个多路复用器每次可以从16路信号中选出4位用作ROM的地址线。每次4位地址从ROM中读出数据,经过相应的移位相加即可,两位计数器用来控制这些多路复位器的输出。

3 FIR滤波器的FPGA实现

按照第2节所描述的第三种优化方法实现常数乘法器,乘法器输出以后按照图4所示的滤波器结构,通过流水线技术的加法器可以实现高效的滤波器。值得注意的是:在乘法器输出的时候需要对输出的数据进行一位扩展,可以避免加法器的溢出问题。

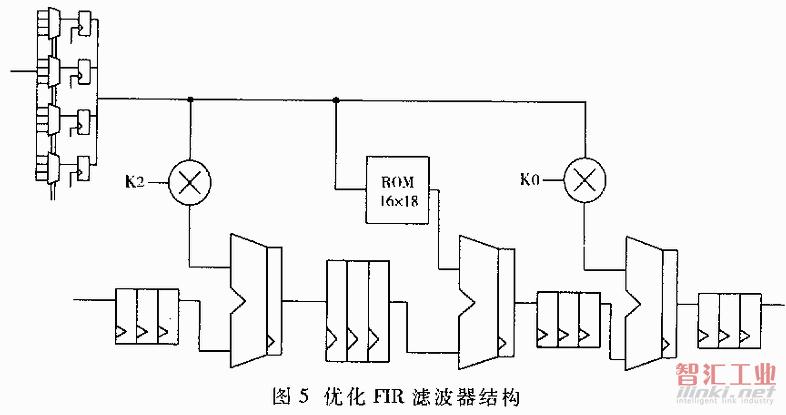

为了有效地利用资源,先通过多路复用器将输入的序列复选出来,这样所有常数乘法器可以共用一个多路复用器,然后通过ROM查表方法实现常数乘法器。优化后的原理结构如5所示。

4 FIR滤波器的电路设计与仿真结果

在数字滤波器设计时,首先根据滤波器的频率特性,选定滤波器的长度和每一节的系数。就目前的设计手段而言,对节数和系数的计算可以采用等波动REMEZ逼近算法编程计算。但是,目前最好的方法还是使用使用的EDA软件来完成。在选择了设计方法和设计要求后,计算出各节系数,并以图形的直观形式显示幅频、相频、冲激响应和零极点图。

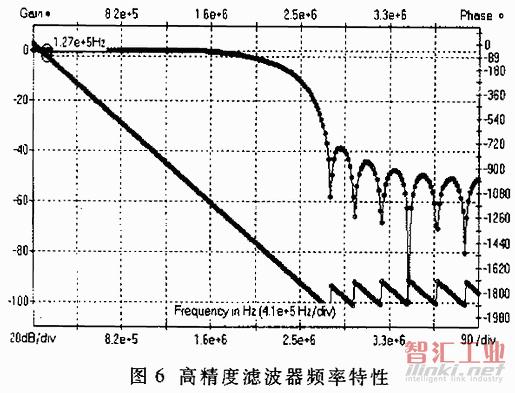

图6是一个采用等波动设计方法生成的均方根升余弦(RRC)FIR滤波器的频域特性。其中,滚降系数为0.35,输入数据率是2.048MHz。

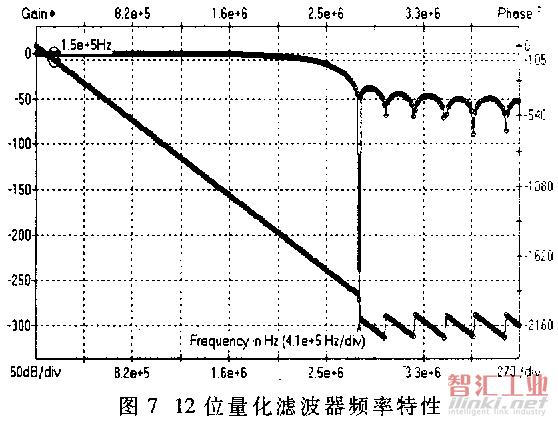

由于在数字滤波器中,各节系数字长有限,所以还要对计算出来的实系数进行量化处理,即浮点数向定点数转换。系数量化后的频域特性如图7所示,量化字长为12。

比较图6与图7,不难看出,系数在量化前后的频域特性是不同的,量化带来了频域特性的恶化。在验证了量化后的频域特性满足设计要求和系数的有效性之后,就可以进行FPGA电路的设计。

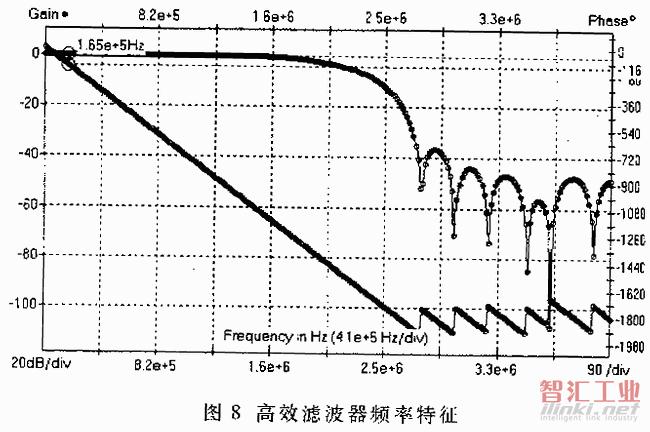

笔者采用流水线技术,根据得到的滤波器系数用VHDL语言编写了滤波器程序。为了充分利用FPGA中四输入查找表的电路结构,一般采用每8节为滤波器的一个基本单元。设计中通过采用流水线技术提高速度,对于更多阶数滤波器的设计,可以采用扩展的方法来实现。仿真结果如图8所示。

本文介绍了并行高效数字滤波器的设计方法,给出了电路的仿真结果。利用VHDL语言,采用可重复配置的FPGA,降低了设计成本,提高了系统的适用性。由于FIR滤波器的系数是常数,可以保存在ROM中,在运算的通过查找表的方法可很快得到乘法输出,减少了使用的资源和布线延时,节省了运算时间。在设计中,充分利用先进的EDA团体操,大大提高了设计效率。

Copyright © 2015 ilinki.net Inc. All rights reserved. 智汇工业版权所有

电话:010-62314658 邮箱:service@ilinki.net

主办单位:智汇万联(北京)信息技术有限公司

主办单位:智汇万联(北京)信息技术有限公司