0 引言

数控系统的开放化是数控技术发展的一个重要方向。这个开放性包括功能的可定制和底层设备通信总线接口的开放性。借助开放化数控系统概念平台,可在功能及性能等方面全面提升数控系统的延展空间。传统的数控系统采用的是并行传输控制模式,这种模式在目前一般的数控加工领域可行,但面对联动轴数不断增加、功能扩展不断增多、各轴空间距离的不断拓展等诸多更新的要求,这种传统的工作模式就很难满足要求。此外,传统数控系统一般通过模拟信号线、脉冲信号线、RS232串行通信等方式来实现底层通信功能。这不仅效率低、而且可靠性差,成为阻碍数控系统性能提高的瓶颈。设计具有高速率、高实时性和高可靠性的计算机实时网络数控系统,从而解决底层通信与控制问题,成为必然趋势。

1 基于光纤的串行通信数控系统特点

基于光纤的串行通信数控系统可以有效解决传统数控系统存在的上述问题。

首先,在功能方面,通过设立主站点控制器,借助光纤通信将各从站被控单元逐个串接起来,从而形成一个网络。站点之间由于可以通过光纤线路连接,空间距离的延伸拓展非常容易。从站站点个数理论上限为127个,这使得联动轴数也得到可观的扩充。通过在主从站点之间制定通信协议,后续扩展功能可在基本通信协议的基础上不断添加完善,非常灵活。

其次,在性能方面,光纤通信是近年来发展十分迅速的新兴技术,拥有很多更具优势的特性,如:通信容量大、传输距离远;信号串扰小、保密性能好;抗电磁干扰、传输质量佳;光纤尺寸小、重量轻,便于敷设和运输等。其中,高速可靠的数据传输为数控系统性能精度的提高提供了保障。

2 系统底层硬件架构

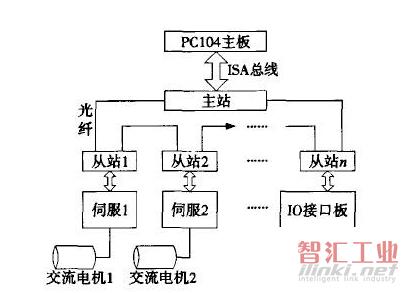

基于光纤通信的数控系统底层总体架构如图1所示。系统采用研祥智能科技有限公司的PCI04主板作为核心控制器,该主板具有如下特点:支持133MHZ前端系统总线,最大内存容量高达512MB,为高速数据处理提供了可靠保证;集成了S3 Graph.ics ProSavage4 2D/3D图形加速控制器,支持CRT和LCD显示,方便数控界面的显示;外围接口丰富,集成了CompactFlash接口、PS2键盘/鼠标接口、USB接口、并口,串口等,便于外接扩展功能设备。

图1基于光纤通信的数控系统底层架构

主从站均用Ahera公司的Cyclone系列FPGA芯片作为通信协议控制芯片,光纤环路数据传输接口则采用武汉电信器件有限公司的LVPECL光收发合一模块。另外,FPGA芯片的控制信号及伺服反馈信号均通过光电耦合隔离处理。

3 串行通信协议设计

3.1 串行通信协议架构

通信协议采用自顶向下的分层模块化设计思想及主从协议分离设计思想。协议总共分为4层:物理层、数据链路层、网络层、应用层。物理层介于通信介质和数据链路层之间,处理传输的各种物理信号,包括电信号、光信号等,使得数据链路层与介质无关。增加协议的适应性。具体完成的功能包括:与数据链路层接口对接、数据的编解码、数据的并串转换、数据过采样或数据时钟恢复、数据字对齐等。

数据链路层完成数据帧的封包和拆包、CRC校验,超时重发,出错重发机制,握手机制,发送各种数据类型之间的互斥机制等。总之,对网络层而言,该层应该是透明化的。

网络层负责同步、计时,总线拥有权切换,数据转发开关的切换。将通过ISA总线发送的数据打包,添加目的站和源站地址信息;将上传给ISA总线的信息进行地址信息解析并缓存数据,等待ISA总线读取。协议采用的编址方式为静态编址,即通过外部硬件设置站点地址。当发送广播地址时,各站点均接收数据。

应用层相当于硬件抽象层或软硬件协同设计抽象层,主要是根据硬件功能,抽象出一个个的C函数接口,供应用软件调用。

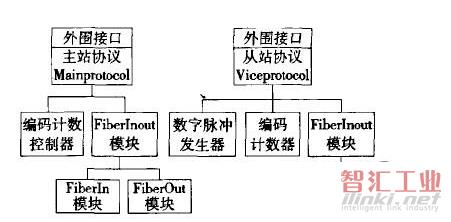

物理层主要用光纤信号输入处理模块Fiberln和光纤信号输出处理模块FiberOut来封装;数据链路层用Fiberlnout模块来封装,它调用了前面两个模块并加上链路层的其他功能;在网络层,主站用Mainprotocol封装,从站用ViceProtocol来封装。应用层实现的功能相对不多,分别在主站模块及CNC系统软件层实现。主从站协议实现的总体架构如图2所示。

图2主从站协议架构

3.2 协议通信的主要实现过程

串行通信协议采取时分复用的介质访问控制方式。在通信周期内,分配给各站点的时间长度固定。系统的周期数据(实时数据)和非周期数据(非实时数据)传输时采用一致的工作时序,每个站的时间片起始位置在时序上是固定的,一个单位时间内完成一次主站数据的传输或者伺服数据的反馈。主站时间片起始时刻位于通信周期的开始,紧随同步信号之后。从站时间片长度设为单位时间片长度,从站的起始时刻根据自身ID号计算获得。

通信周期时间片的分配如图3所示。

图3通信周期时间片分配

光纤通信环路内,主站与从站数据通信处理的具体实现过程如下:

(1)系统上电,主站数据处理模块、各从站数据处理模块内部所有通信协议模块均初始化。

(2)主站等待来自处理器的相关指令,当收到数据传输指令后,主站进入下一步工作阶段。

(3)主站测试通信环路是否畅通,给整个环路发送检测信号,若主站能十次正确接收到,则测试成功。主站进入下一步工作阶段,否则产生错误中断,并返回到步骤(2)。

(4)主站向通信环路广播同步信号,各个从站同时收到同步信号,同步信号在环路传输一圈,若最终主站能够收到自己发出的同步信号,表示环路站点同步成功,进入下一步工作阶段;若主站不能收到自身发出的同步信号,将再次发送同步信号,连续十次同步失败,则主站产生相应的出错中断,并返回步骤(2)。

(5)主站和各个从站收到同步信号时,一个数据传输周期开始,主站和各个从站的时间计数器模块开始计数,在通信周期内,各个站根据自己的地址和当前计数值,确定哪个时间槽属于该站点,当属于自己的时间槽到来时,该站点便拥有总线的数据发送权,向总线发送数据;数据传输周期开始后,主站在属于自己的时间槽内往从站发送数据。与此同时,主站接收ISA总线数据并对数据进行标志、缓存,完成数据的编码,实现握手机制,超时重发、出错重发,对发送数据进行并串转换及对接收的数据进行串并转换。

(6)主站发送一帧数据后,等待相应从站的应答信号,若收到从站的负应答信号,表示数据没有被从站正确接收,主站将重发上一帧数据并再次等待从站的应答信号,若连续两次收到从站的负应答信号,则产生错误中断并返回步骤(2);若收到从站的正应答信号,表示数据被从站正确接收,主站在自己的时间槽内继续发送下一帧数据,若没有新的数据发送则等待该时间槽的结束。

(7)主站时间槽结束后,从站在属于自己的时间槽内往主站发送数据,从站发送一帧数据后,等待主站的应答信号,若收到主站的负应答信号,表示数据没有被主站正确接收,从站将重发上一帧数据并再次等待主站的应答信号,若连续两次收到主站的负应答信号,从站产生错误中断并返回等待新一次的同步信号;若收到主站的正应答信号,表示数据被主站正确接收,从站在自己的时间槽内继续发送下一帧数据,若没有新的数据可以发送则等待该时间槽的结束。

(8)主站和各个从站的时间计数器模块计数到设定值时,当前数据传送周期结束,主站返回步骤(2),等待处理器指令或开始下一次数据传送周期,从站等待主站的同步信号。

以上阶段依次进行,不断循环,直到控制器终止传输或者环路传输错误被迫中断。

3.3 数据编码特点

在曼彻斯特编码和差分曼彻斯特编码中,每位中间都有一次电平跳变,因此波特率是数据速率的2倍。对于lOOMbps的高速网络,若采用该类编码方式,就需要200M的波特率,硬件成本是lOOM波特率硬件成本的5-10倍。

本系统的通信协议直接对基带进行编码,以适合光纤作为通信介质的传输方式。为提高编码效率,尽量减小硬件开销,同时方便同步信号的提取,这里采用4B/5B码对源码进行编码。例如,用于同步的报文起始符为连续的15个0,通过4B/5B编码可以有效地消除源码中可能存在的这种码组。4B/5B编码的规则如表1所示。

5位二进制代码的状态共有25=32种,从中取1的个数不少于2个的状态来表示0~F,这样就可以保证在介质上传输的代码能提供足够多的同步信息。

4 联合通信仿真及结果分析

在QuartusU6.0软件环境下设计好主从站各模块VHDL代码。为模拟主从站通信,设计一个新的顶层文件调用主从站模块,用该模块调用1个主站、3个从站。通过该顶层文件,仿真主站与3从站之间的数据通信。

仿真时,由主站给各从站发送数据,各从站接收到相应的数据后,立即将接收到的数据重新发送给主站。根据各从站接收到的数据和主站接收到的数据,可以判断环路通信是否正常。

主站发往从站1、从站2、从站3的数据分别初始化为随后发送的数据则循环左移一位,发送时间间隔略大于通信周期,为100us(设置的协议通信周期为90us)。由结果可知,该通信协议能准确无误地实现主从站点间的数据传输。根据设计,该通信协议能够达到的最高有效数据传输速率为5.33Mb/s。如果对系统时钟进行倍频处理,该速率还可以进一步提高,如:系统时钟频率提高至150MHZ,最高有效数据传输速率为8Mb/s。

5 结束语

本文通过设计串行通信协议,并借助FPGA构建主从站,仿真实现了数控系统中基于光纤的环路高速串行通信。该设计目前已经在实际数控系统中得到成功运用,其简便灵活、高实时高稳定的性能很好地解决了传统数控系统存在的不易扩展、通信可靠性不高等问题。该设计为数控系统的开放性研究提供了一个很好的发展方向,后期可进一步通过优化VHDI.代码,改善通信部分细节,缩短通信周期等方式提高其通信性能。

(审核编辑: 智汇胡妮)