更高的数据速率和更复杂的功能正在增加超大规模数据中心、人工智能和网络应用程序的SoC大小。当SoC尺寸接近最小分划线尺寸时,设计者被迫将SoC拆分成更小的晶粒,以获得更高的生产良率并降低总成本。此类soc中的Die-to-Die互连,要求不能影响整个系统的性能,并且要低延迟、高能效和高吞吐量。这些要求推动了对高吞吐量晶粒间(Die-to-Die)的物理需求。

超大规模数据中心、人工智能(AI)和网络应用的SoC设计人员面临着大数据时代以来的诸多挑战。由于工作负载需求和更快地移动数据的需要,此类soc已经变得更加复杂,具有更高级的功能,并达到了最大的网线大小。因此,设计人员将soc划分到多芯片模块(MCM)封装中的较小模块中。为了支持具有高数据速率的晶粒连接,这些分散的芯片需要超短的连接。除了带宽之外,晶粒间的连接必须确保可靠,并且具有极低的延迟和电源效率。本文描述了几个不同的晶粒间连接用例,以及在搜索用于晶粒间连接的高速PHY IP时需要考虑的基本事项。

在MCM封装中出现了用于模块间连接的新用例,其中包括:

高性能计算和接近最大网线大小的服务器soc

超过最大网线尺寸的以太网交换机和网络soc

基于分布式SRAM的人工智能(AI) soc来扩展复杂的算法

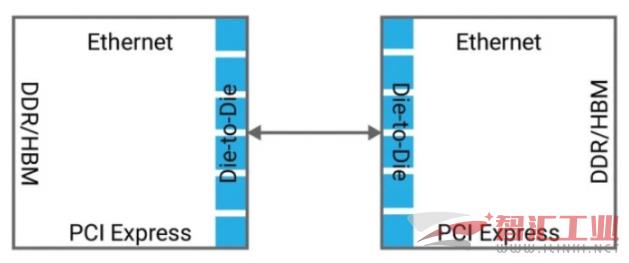

高性能计算和服务器SoC的规模越来越大,可达到550mm2到800 mm2,从而减少了SoC的产量,但增加了每个芯片的成本。优化SoC良率的一个更好的方法是将SoC分成两个或多个等价的同质模组,如图所示,并使用一个晶粒间 PHY IP连接这些模组。在这样的用例中,最关键要保证极低的延迟和零误码率,因为较小的晶粒必须描述和表现为单个晶粒。

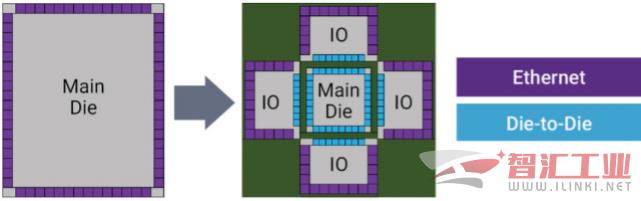

以太网交换机SoC是数据中心的核心,它必须以更快的速度将数据从12 Tbps移动到25 Tbps,而这需要100G SerDes接口的256条通道,这不太可能在800 mm2的网线区域内容纳SoC。为了克服这一挑战,设计人员将SoC分解为一个配置,其中核心晶粒被I/O 晶粒包围,如下图所示。然后使用晶粒间的收发器将晶圆连接到I/O模上。

在这个用例中,只有当晶粒间收发机的带宽密度远远优于I/O模中的长范围并行转换器SerDes时,晶粒切割才有效。因此,关键参数是每毫米的晶粒边带宽(Die-edge bandwidth)密度。

晶粒间连接的以太网交换机SoC的示例

所有这些用例中,用于Die之间连接的理想高速PHY可以简化MCM封装要求。由于每条通道的高吞吐量可达112 Gbps,因此相对有限的通道数可以实现非常高的总吞吐量。在这种情况下,在这种情况下,封装跟踪间距和堆栈可以是保守的(L/S为10u/10u最常见)。在这些用例中,还可以使用传统低成本、基于有机基质的封装。

高速物理层IP对Die之间连接的要求

光互连论坛(OIF)正在定义用于数据速率高达112 Gbps的超短连接(USR)和超短连接(XSR)传输的电I/O标准。这些规范定义了Die之间的链接和Die之间的光学引擎,它与SoC位于同一封装内,这大大降低了功耗和复杂性,并具有非常高的吞吐量密度。

SoC设计人员在研究MCM中用于芯片间连接的高速PHY IP解决方案时,必须考虑几个基本特性:数据吞吐量或带宽、能源效率(以皮焦耳/比特为单位)、延迟(以纳秒为单位)、最大链路长度(以毫米为单位)和误码率。

数据吞吐量或带宽

为了实现与其他收发器的互操作性,Die之间的IP必须确保符合USR和XSR链路相关的OIF电气规范。支持脉冲幅度调制(PAM-4)和不归零(NRZ)信令对于满足这两种链路要求并实现每路最大112 Gbps的带宽至关重要。这种信令会导致非常高的带宽效率,这是一个关键的要求,因为在MCM的晶粒之间传输的数据量非常大。数据移动速度通常在每秒兆位级别,这限制了分配给USR和XSR链路的芯片边缘的大小。

然而,同样重要的是支持广泛的数据速率。通常,如果数据速率与内部结构中使用的数据或者支持Die之间协议所需的所有数据速率一致,那么实现Die之间的链接是最好的。例如,即使在32 Gbps这样的高速下,PCIe在协议初始化时也必须支持将数据速率降至2.5 Gbps。

链接

在Die之间中,大量的数据必须通过晶粒间隙的短数据路径。为了保证晶粒放置在封装基板上的最大灵活性,PHY IP必须支持TX和RX之间的距离要达到50毫米。

能源效率

能源效率成为一个重要的因素,特别是在SoC功能被分割成多个同类晶粒的情况下。在这种情况下,设计人员会寻找在不影响SoC总功率预算的情况下,在Die之间传输大量数据的方法。理想的Die之间IP提供的能量效率比每比特(1pJ/bit)或1mW/Gbps更好。

延迟和误码率

为了使Die之间的连接“透明”,延迟必须非常低,同时必须优化误码率(BER)。对于简化的体系结构,Die之间PHY IP本身要实现超低延迟,BER优于10e-15。根据链路范围的不同,互连可能需要使用前向纠错(FEC)机制来保护,以实现如此低的误码率。FEC延迟影响着解决方案的总体延迟。

宏观布局

除了这些与性能相关的参数外,PHY IP还必须支持芯片的所有侧面的布置,以实现芯片以及MCM的有效布局。通过对宏的优化,可以实现低耦合的高效晶粒间路由,优化晶粒和MCM区域,最终提高功率效率。

在选择一个Die之间的IP时,还有许多其他因素要考虑,包括可测试特性,这保障在封装之前对晶粒进行生产测试,但以上是最基本的。

(审核编辑: 智汇婷婷)